Одним из самых важных элементов современных LCD-панелей является, так называемый, Timing Controller – TCON. Микросхемой TCON осуществляется преобразование сигналов, полученных от видеоконтроллера в сигналы управления столбцовыми драйверами LCD-матрицы. В подавляющем большинстве случаев микросхема TCON входит в состав LCD-панели, т.е. образует вместе с матрицей единый неразборный модуль, и является практически недоступной для диагностики и, тем более, для ремонта. К тому же, вероятность отказа этой микросхема достаточно низка. Но в то же самое время существует значительное количество LCD-панелей, в которых электронная «начинка» доступна, и в случае неисправности ЖК-панели, вполне реально обеспечить более тонкую диагностику на уровне сигналов и отдельных микросхем. Кроме того, знание принципов функционирования контроллера TCON позволит специалистам подходить к ремонту LCD-мониторов более осмысленно и профессионально.

Для начала стоит напомнить нашим читателям некоторые аспекты построения LCD-панелей. Так как современные экраны мониторов образованы матрицами на жидких кристаллах (ЖК), состоящими из большого числа отдельных ячеек, реализовать прямую адресацию всех этих ячеек физически невозможно. Так, например, цветная матрица с разрешением 1600х1200 точек содержит 5.760.000 ячеек ([1600х3]х1200), т.е. для управления ею требуется почти 6 миллионов ключей и столько же управляющих сигналов.

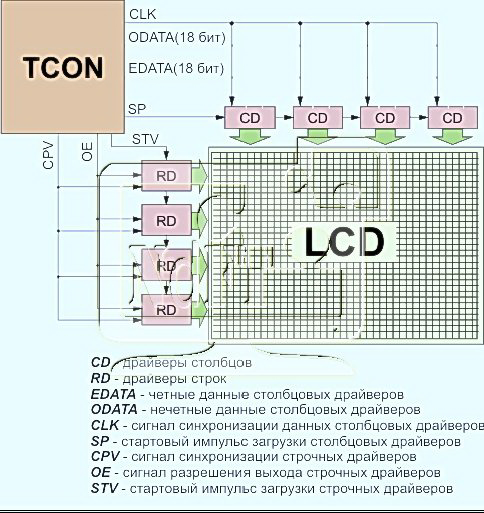

Единственным выходом при реализации ЖК-панели с большим числом элементов изображения является мультиплексирование. Это значит, что элементы изображения (пикселы, точки) находятся на пересечении системы электродов строк (Row) и столбцов (Column). При этом количество элементов управления значительно уменьшается. Если вернуться к нашему примеру, то при использовании матрицы с разрешением 1600х1200 точек, требуется 4800 столбцовых ключей и 1200 строковых ключей. Для повышения технологичности изделия и снижения массогабаритных характеристик строчные и столбцовые ключи имеют, чаще всего, интегральное исполнение, т.е. выполнены в виде микросхем. Такие микросхемы получили название драйверов строк и драйверов столбцов. Типовая блок-схема модуля управления графическим ЖК-дисплеем показана на рис.1.

Рис. 1

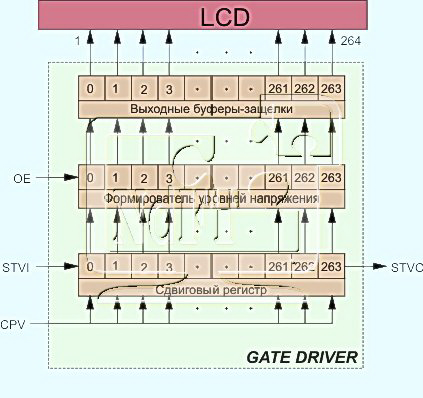

Драйверы строк (Row Driver – RD) содержат сдвиговый регистр на N-разрядов, схему преобразования логических уровней в уровни напряжения для управления строками, а также схему управления сменой полярности. В начале кадра в регистр записывается логическая «1». По фронту или спаду сигнала строчной развертки эта единица сдвигается в следующий разряд регистра до тех пор, пока не достигнет последнего разряда. Для наращивания разрядности может использоваться несколько микросхем драйверов строк (метод каскадирования). При каскадировании используется эстафетный механизм, который заключается в следующем: как только в последнем разряде сдвигового регистра появится логическая «1», будет активизироваться микросхема следующего драйвера, т.е. следующим импульсом сигнала строчной развертки эта единица переходит в первый разряд сдвигового регистра следующего драйвера строк.

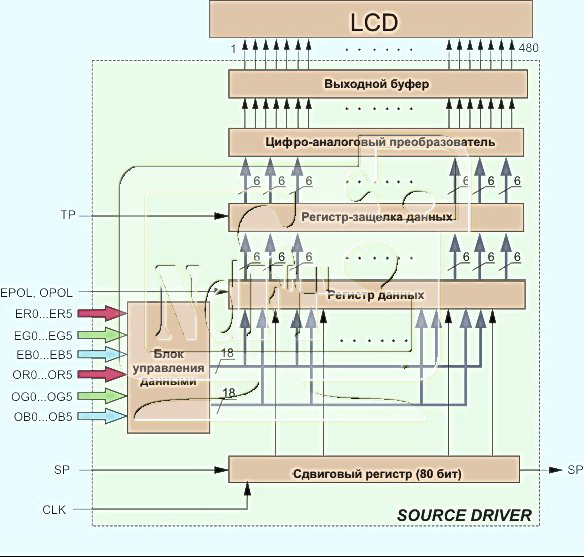

Драйверы столбцов (Column Driver – CD) построены по другой схеме. Эти драйверы содержат M-разрядный регистр, запись в который может производиться по шине с различной разрядностью. Эта шина может быть и одноразрядной (предельно-простой случай), а может быть и 2-, 4-, 8-разрядной. В современных же микросхемах драйверов столбцов, предназначенных для ЖК-панелей с высоким разрешением, шина может быть и 18 и 36-разрядной. По сигналу строчной развертки данные из буферного регистра переписывается в выходной регистр. Логические уровни выходного регистра преобразуются в рабочие уровни напряжений для управления столбцами графического ЖК-дисплея. Такое преобразование осуществляется схемой смещения, входящей в состав столбцового драйвера.

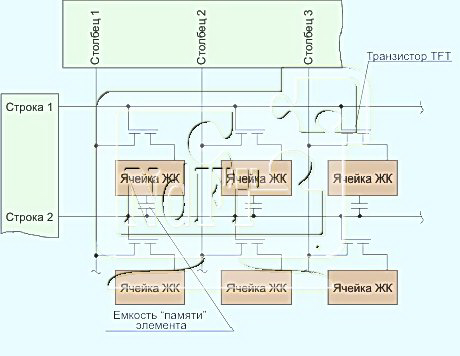

Большая часть современных мониторов производится на основе матриц с активной адресацией, в которых на пересечении строки и столбца имеется ключевой нелинейный элемент – тонкопленочный транзистор (TFT – Thin Film Transistor). Топология матрицы с активной адресацией показана на рис.2.

Рис. 2

Как видно из этого рисунка, для управления транзистором TFT необходимо обеспечить формирование определенных уровней напряжения на его затворе (GATE) и на его стоке (SOURCE). И из этого же рисунка видно, что столбцовыми драйверами формируются напряжения стока, а драйверами строк обеспечивается формирование напряжений затвора. Поэтому при описании элементной базы LCD-панелей типа TFT понятие столбцового драйвера заменяется термином драйвера стока (Source Driver), а вместо драйвера строки вводится термин драйвер затвора (Gate Driver).

Управление драйверами срок и столбцов осуществляется микросхемой контроллера синхронизации – Timing Controller (TCON). Иногда в литературе микросхему ТCON называют дисплейным контроллером. Как уже говорилось ранее, микросхемой TCON обеспечивается прием и преобразование данных от видеоконтроллера, и перераспределение этих данных по микросхемам драйверов строк и столбцов (рис.3). Как правило, драйверы строк и столбцов ЖК-панели с достаточно высоким разрешением состоят из нескольких микросхем, образующих каскадное соединение.

Рис. 3

Одним из представителей микросхем класса TCON является микросхема SN75LVDS88, разработанная и производимая корпорацией Texas Instruments. Эта микросхема TCON имеет внешний интерфейс LVDS, что, кстати, и следует из маркировки микросхемы. Если быть более точным, то для передачи данных от видеоконтроллера на TCON используется интерфейс FlatLinkTM, являющийся одним из вариантов LVDS. Классический вариант LVDS и его разновидность FlatLinkTM представляет собой четыре пары дифференциальных сигналов для передачи сигналов красного, синего и зеленого цветов, а четвертая дифференциальная пара используется для передачи сигналов синхронизации.

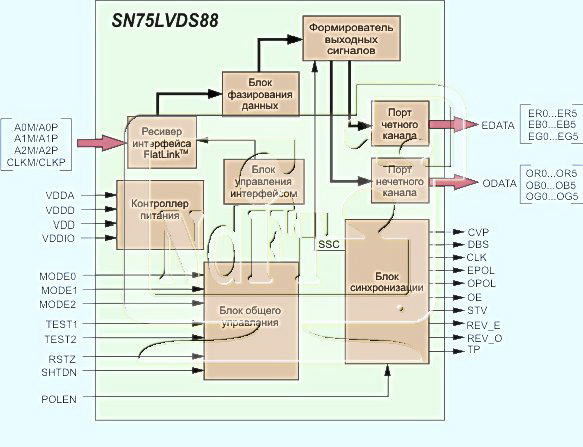

Микросхема SN75LVDS88 традиционно входит в состав LCD-панели и ее функциональным назначением является обеспечение интерфейса между внешним графическим контроллером и TFT-матрицей. Общая блок-схема контроллера SN75LVDS88 представлена на рис.4.

Рис. 4

К особенностям этой микросхемы можно отнести:

– 6-разрядный системный интерфейс;

– поддержка разрешающей способности стандарта XGA;

– поддержка основного потока данных и данных драйверов затвора (Gate Driver);

– наличие дополнительных контактов конфигурации;

– построение по низковольтной технологии CMOS с питающим напряжением 3.3 В;

– наличие входа ФАПЧ c частотой 65 МГц;

– реализация в 100-контактном корпусе типа TQFP;

– устойчивость к электростатическим разрядам величиной до 4 кВ по контактам шины LVDS, все остальные выводы микросхемы выдерживают электростатические разряды до 2кВ;

– повышенная устойчивость к электромагнитным помехам.

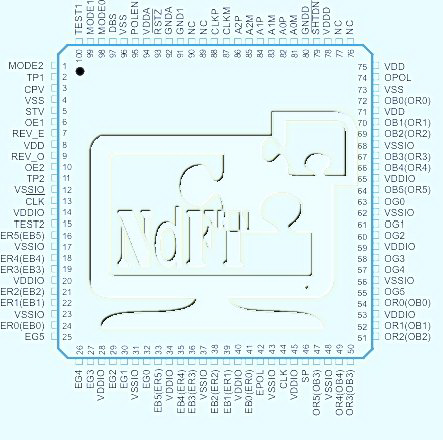

Цоколевка корпуса микросхемы SN75LVDS88 представлена на рис.4, а назначение сигналов описывается в табл.1.

Таблица 1.

Обозначение | № контакта | Вход/Выход | Описание |

A0M/A0P | 81, 82 | Вход | Дифференциальная пара (первая) входных сигналов интерфейса FlatLinkTM для передачи последовательного потока данных одного из цветов (R, G, B) от внешнего графического контроллера. |

A1M/A1P | 83, 84 | Вход | Дифференциальная пара (вторая) входных сигналов интерфейса FlatLinkTM для передачи последовательного потока данных одного из цветов (R, G, B) от внешнего графического контроллера. |

A2M/A2P | 85, 86 | Вход | Дифференциальная пара (третья) входных сигналов интерфейса FlatLinkTM для передачи последовательного потока данных одного из цветов (R, G, B) от внешнего графического контроллера. |

CLK | 44 | Выход | Сигнал тактовой частоты для столбцовых драйверов. Этим сигналом тактируется загрузка в регистры столбцовых драйверов данных, формируемых на выходах ER0-ER5, OR0-OR5, EB0-EB5, OB0-OB5, EG0-EG5, OG0-OG5. |

CLK# | 13 | Выход | Сигнал тактовый частоты для столбцовых драйверов, сдвинутый по фазе на 180° относительно сигнала CLK. |

CLKM/CLKP | 87, 88 | Вход | Дифференциальная пара входных сигналов интерфейса FlatLinkTM. Эта пара используется для передачи тактовых сигналов интерфейса LVDS. |

CPV | 3 | Выход | Сигнал тактовой частоты, используемый для управления драйвером строк (Gate Driver). |

DBS | 97 | Вход | Входной сигнал, используемый для управления последовательностью данных, передаваемых на столбцовые драйверы. При установке этого сигнала в низкий уровень (лог.0), контроллером TCON на выходе формируется нормальная последовательность сигналов цвета для загрузки столбцовых драйверов (сначала передаются данные красного, затем зеленого и потом уже синего цвета – RGB). При установке сигнала DBS в высокий уровень (лог.1) контроллером TCON обеспечивается формирование обратного порядка сигналов цвета – BGR – для загрузки столбцовых драйверов. |

EPOL | 42 | Выход | Сигнал, являющийся индикатором «полярности» выходных сигналов четного канала данных для столбцовых драйверов (ER0-ER5, EB0-EB5, EG0-EG5), т.е. этот сигнал показывает, каким уровнем активны сигналы четного канала данных – высоким или низким. |

ER0…ER5 (EB0…EB5) | 24, 22, 21 19, 18, 16 | Выход | Выходная 6-разрядная шина четных данных красного цвета, при условии, что используется нормальная последовательность загрузки столбцовых драйверов (RGB), т.е. когда сигнал DBS установлен в низкий уровень. При «обратном» порядке сигналов цвета (BGR), т.е. при высоком уровне сигнала DBS, эти выводы используются для передачи данных синего цвета. |

EB0…ER5 (ER0…ER5) | 41, 39, 38 36, 35, 33 | Выход | Выходная 6-разрядная шина четных данных синего цвета, при условии, что используется нормальная последовательность загрузки столбцовых драйверов (RGB), т.е. когда сигнал DBS установлен в низкий уровень. При «обратном» порядке сигналов цвета (BGR), т.е. при высоком уровне сигнала DBS, эти выводы используются для передачи данных красного цвета. |

EG0…EG5 | 32, 30, 29 27, 26, 25 | Выход | Выходная 6-разрядная шина четных данных зеленого цвета. |

OPOL | 74 | Выход | Сигнал, являющийся индикатором «полярности» выходных сигналов нечетного канала дан-ных для столбцовых драйверов (OR0-OR5, OB0-OB5, OG0-OG5), т.е. этот сигнал показывает, каким уровнем активны сигналы нечетного канала данных – высоким или низким. |

OR0…OR5 (OB0…OB5) | 54, 52, 51 50, 49, 47 | Выход | Выходная 6-разрядная шина нечетных данных красного цвета, при условии, что используется нормальная последовательность загрузки столбцовых драйверов (RGB), т.е. когда сигнал DBS установлен в низкий уровень. При «обратном» порядке сигналов цвета (BGR), т.е. при высоком уровне сигнала DBS, эти выводы используются для передачи данных синего цвета. |

OB0…OR5 (ER0…ER5) | 72, 70, 69 67, 66, 64 | Выход | Выходная 6-разрядная шина нечетных данных синего цвета, при условии, что используется нормальная последовательность загрузки столбцовых драйверов (RGB), т.е. когда сигнал DBS установлен в низкий уровень. При «обратном» порядке сигналов цвета (BGR), т.е. при высоком уровне сигнала DBS, эти выводы используются для передачи данных красного цвета. |

OG0…OG5 | 63, 61, 60 58, 57, 55 | Выход | Выходная 6-разрядная шина нечетных данных зеленого цвета. |

GND1 | 91 | — | «Общий». |

MODE 0, 1, 2 | 98, 99, 1 | Вход | Сигналы, задающие режим работы контроллера TCON «по-умолчанию». |

OE1, OE2 | 6, 10 | Выход | Сигналы, разрешающие работу строчных драйверов. |

POLEN | 95 | Вход | Сигнал, разрешающий или запрещающий управление «полярностью» выходных данных, а также разрешающий индикацию полярности выходных данных с помощью сигналов EPOL и OPOL. |

REV_E | 7 | Выход | Сигнал, управляющий инвертированием точек или строк столбцовых драйверов для четных данных. |

REV_O | 9 | Выход | Сигнал, управляющий инвертированием точек или строк столбцовых драйверов для нечетных данных (сигнал смещен по фазе на 180° относительно сигнала REV_E). |

RSTZ# | 93 | Вход | Сигнал сброса контроллера. Сигнал активен низким уровнем. |

SHTDN# | 79 | Вход | Сигнал отключения контроллера. Сигнал активен низким уровнем. |

SP | 46 | Выход | Стартовый импульс передачи данных для столбцовых драйверов. |

STV | 5 | Выход | Стартовый импульс передачи данных для строчных драйверов. |

TEST1 | 100 | Вход | Вывод тестирования контроллера. Вывод должен быть подключен к «земле». |

TEST2 | 15 | Вход | Вывод тестирования контроллера. Вывод должен быть подключен к «земле». |

TP1, TP2 | 2, 11 | — | Выходы управления столбцовыми драйверами. Этими сигналами обеспечивается «защелкивание» преданных данных в выходном регистре столбцового драйвера и разрешаются выходы столбцовых драйверов. |

VDDA | 94 | — | Напряжение питания аналоговой части модуля LVDS контроллера TCON. |

GNDA | 92 | — | «Общий» для аналоговой части модуля LVDS. |

VDDD | 78 | — | Напряжение питания цифровой части модуля LVDS контроллера TCON. |

GNDD | 80 | — | «Общий» для цифровой части модуля LVDS. |

VDD | 8, 71, 75 | — | Напряжение питания. |

VSS | 4, 73, 96 | — | «Общий». |

VDDIO | 20 | — | Напряжение питания формирователей выходных сигналов. |

VSSIO | 23 | — | «Общий» для формирователей выходных сигналов. |

NC | 76, 77, 89, 90 | — | Выводы не подключены и не используются. |

По структурной схеме и по сигналам, описанным в табл.1, стоит сделать некоторые замечания, позволяющие лучше представить работу контроллера TCON и функциональное назначение отдельных сигналов.

В структуре TCON SN75LVDS88 можно выделит несколько основных блоков.

1. Модуль интерфейса FlatLinkTM. Ядром модуля интерфейса является ресивер семейства SN75LVDS86А. Этим ресивером обеспечивается прием трех последовательных потоков данных, описывающих значение цвета. Каждому из трех основных цветов соответствует своя дифференциальная пара сигналов (A0M/A0P, A1M/A1P, A2M/A2P), по которой и передаются данные в TCON. Ресивер обеспечивает преобразование полученных последовательных данных к параллельному виду для дальнейшего преобразования сигналов. Четвертая дифференциальная пара (CLKM/CLKP) используется для передачи тактового сигнала, необходимого для корректного преобразования последовательного пока данных в параллельный вид. Основными элементами ресивера являются четыре сдвиговых регистра с последовательной загрузкой и параллельным выходом.

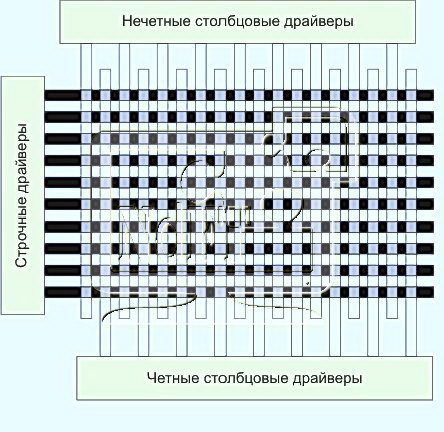

2. Блок фазирования данных. Этим модулем обеспечивается обработка данных, полученных от ресивера шины LVDS. Блок фазирования поддерживает архитектуру двойной шины столбцовых драйверов. При такой архитектуре на выходе TCON имеется два порта, управляющих столбцовыми драйверами, а все выходные точки делятся на четные (Even) и нечетные (Odd). Эти четные и нечетные точки распределяются между двумя выходными шинами данных (EDATA и ODATA), подключенных к вышеупомянутым двум портам. При разбиении столбцов на четные и нечетные можно, например, применить такой вариант топологии матричной структуры, как это показано на рис.5. Такая топология дает возможность использовать более широкий шаг выводов для присоединения столбцовых драйверов без изменения шага столбцов самой матрицы.

Рис. 5

3. Формирователь выходных сигналов. Этим модулем обеспечивается выдача данных для управления столбцовыми и строчными драйверами. При формировании выходных сигналов предпринимается целый ряд мер для уменьшения электромагнитных помех радиочастотного диапазона. К таким мерам относятся, в частности, и разбиение данных на два канала (четные и нечетные данные), и возможность изменения «полярности» выходных сигналов, и инвертирование данных для соседних точек или строк.

4. Блок синхронизации. Блоком синхронизации формируется целый ряд синхронизирующих сигналов и сигналов управления драйверами строк и столбцов:

– SSC (Source Shifted Clock) – внутренний сигнал сдвига данных столбцовых драйверов. Основной сигнал тактовой частоты должен быть подстраиваемым с целью обеспечения предусмотренной задержки по фазе относительно выходных сигналов. Это позволяет проектировать систему, правильно настроенную на реальную частоту фиксации данных в столбцовых драйверах. В результате, можно получить систему, работающую стабильно, независимо от параметров внешних элементов, размещенных на печатной плате.

– SP (Starting Pulse) – стартовый импульс загрузки столбцовых драйверов. При каскадном включении столбцовых драйверов этот сигнал является эстафетным, т.е. передается от одного столбцового драйвера к другому. Период следования этих импульсов соответствует потоку данных RGB для одной строки, т.е. этот сигнал формируется в начале каждой строки

– CLK (Clock) – сигнал тактовой частоты, обеспечивающий передачу отдельных «точек» по каналам RGB от TCON в столбцовые драйверы.

– TP – импульсы защелкивания данных для столбцовых драйверов. По этим сигналам данные из буферного регистра столбцового драйвера «защелкиваются» в его выходном регистре, что приводит к выбору соответствующих ячеек LCD-матрицы (рис.6).

Рис. 6

– CPV – импульсы тактовой частоты для драйверов строк. Этим сигналом осуществляется переключение строк LCD-матрицы. Этот сигнал является прямым аналогом сигнала HSYNC в мониторах с ЭЛТ.

– STV – стартовый импульс загрузки строчных драйверов. Сигнал формируется в начале каждого кадра. При каскадном включении строчных драйверов этот сигнал является эстафетным, т.е. передается от одного драйвера строки к другому.

– OE (Output Enable) – сигнал разрешения работы драйвера строки, этим сигналом данные сдвигового регистра фиксируются в выходном регистре-защелке, т.е. данные «защелкиваются» на выходе драйвера строки, что приводит к выбору соответствующих строк (рис.7).